73

Vl ≈ OV

V2≈2.9V

TD = O

TR = O

TF = O

PW= 0.15ms

PER = 0.3ms__

R_B

—Wv

100k

V

Q2N2222

- Q

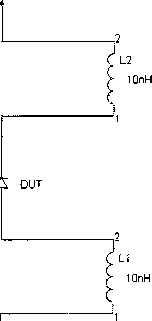

Figure B.5 : Bipolar-junction-transistor (BJT) set up as a common-emitter amplifier

for voltage amplification. Each 3V control signal from the FPGA circuit acts as the

input to one common-emitter amplifier, and the output passes onto each SLM pixel

after being amplified to 16V.

schematic design program, Allegro Design Entry CIS.

4. Export the netlist of the schematics to be used in the PCB layout software,

Allegro Cadence.

5. Layout the exact positions of the components and wires in Allegro Cadence.

6. Send layout files, generated in Allegro Cadence, to a company for PCB fabri-

cation.

7. Purchase parts and send to a company for assembly.

More intriguing information

1. Healthy state, worried workers: North Carolina in the world economy2. THE ECONOMICS OF COMPETITION IN HEALTH INSURANCE- THE IRISH CASE STUDY.

3. Skills, Partnerships and Tenancy in Sri Lankan Rice Farms

4. The name is absent

5. Improvement of Access to Data Sets from the Official Statistics

6. Educational Inequalities Among School Leavers in Ireland 1979-1994

7. Langfristige Wachstumsaussichten der ukrainischen Wirtschaft : Potenziale und Barrieren

8. The name is absent

9. Automatic Dream Sentiment Analysis

10. The East Asian banking sector—overweight?