Yuanbin Guo et al.

13

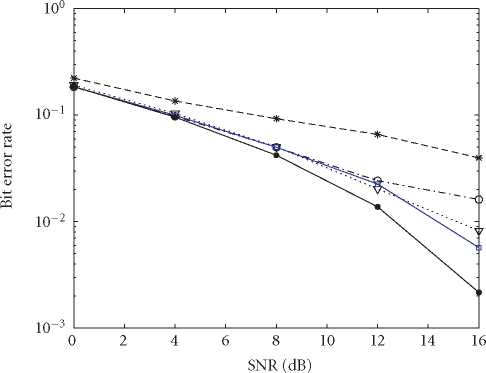

-*- LMS

-O- CG, iter. = 3

∙∙V∙ CG, iter. = 5

FFT-based

DI

Figure 11: BER performance of 2 × 2 in Pedestrian-B channel case 2: K = 10 codes; K = 10, G = 16, Lh = 6, T = 2, M = 2, and F = 10.

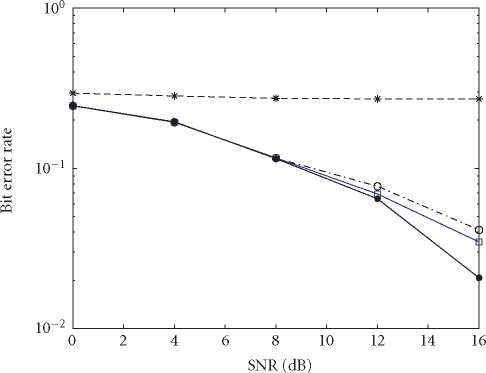

-*- LMS FFT-based

-O- CG, iter. = 5 -→- DMI

Figure 12: BER performance of 4 × 4 in Pedestrian-A channel; K = 12, G = 16, Lh = 3, T = 4, M = 4, and F = 10.

is presented in [13].

However, this type of SoC design space exploration is

very time consuming because the current standard trial-

and-optimize approaches apply hand-coded VHDL/Verilog

or graphical schematic tools. In this section, we present

a Catapult C-based HLS methodology [26] to explore the

VLSI architecture space extensively in terms of the area/time

tradeoff. This is enabled with high-level architecture and re-

source constraints. Synthesizable RTL is generated from a

fixed-point C/C++ level design and imported to the graph-

ical tools for module binding. The proposed procedure for

implementing an algorithm to the SoC hardware is shown

in Figure 14. The number of FUs is assigned according to

the time/area constraints. Software resources such as regis-

ters and arrays are mapped to hardware components and re-

quired finite-state machines (FSMs) necessary for accessing

these resources are generated. In this way, we can study sev-

eral architecture solutions efficiently. In the next step of the

design flow, the generated RTL is imported into the HDL en-

vironment and integrated with other modules of the system,

More intriguing information

1. Computational Batik Motif Generation Innovation of Traditi onal Heritage by Fracta l Computation2. Correlation Analysis of Financial Contagion: What One Should Know Before Running a Test

3. Developments and Development Directions of Electronic Trade Platforms in US and European Agri-Food Markets: Impact on Sector Organization

4. The name is absent

5. The name is absent

6. Monetary Policy News and Exchange Rate Responses: Do Only Surprises Matter?

7. DISCUSSION: ASSESSING STRUCTURAL CHANGE IN THE DEMAND FOR FOOD COMMODITIES

8. The name is absent

9. The name is absent

10. The use of formal education in Denmark 1980-1992