14

EURASIP Journal on Applied Signal Processing

|

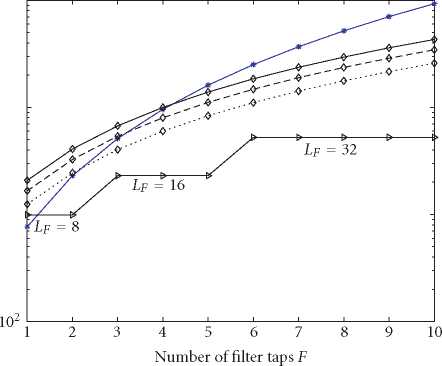

Table 3: The overall tap-solver complexity comparison. | ||

|

Equivalent complex multiplication |

Example | |

|

DMI |

O {( M + NF )( NF )2} |

92928 |

|

CG |

O{ JM [( NF )2 + 5 NF ]} |

43120 |

|

FFT-based |

O {[(N2/2 + 2MN) log2 Lf + (N3 + MN2)]Lf/2} |

5248 |

105

104

103

DMi DMI

→- CG: J = 5

CG:J = 4

■■G- CG: J = 3

—o— FFT-based

Figure 13: Overall tap-solver complexity comparison; algorithm complexity comparison for M = 4, N = 4 tap solver.

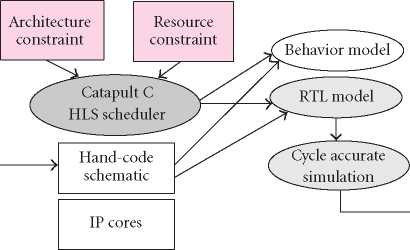

Algorithm

Equations

Floating-point

Fixed-point

Architecture

HDL/

Verilog

Mentor graphics

advantage

modelSim

Matlab

C/C ++

Xilinx ISE

Nallatech

gate/netlist

Figure 14: Integrated Catapult C high-level-synthesis design methodology.

which are either another Catapult C design or a legacy IP

core. Leonardo spectrum is invoked for gate-level synthesis.

Xilinx ISE place & route tool is used to generate gate-level

bit-stream file. Raising the language level may lead to con-

cerns about the architecture efficiency, which highly depends

on the design tool’s capability. To address these concerns,

we have compared both the architecture area/time efficiency

and the achieved productivity in [13] with the conventional

More intriguing information

1. The name is absent2. Dynamiques des Entreprises Agroalimentaires (EAA) du Languedoc-Roussillon : évolutions 1998-2003. Programme de recherche PSDR 2001-2006 financé par l'Inra et la Région Languedoc-Roussillon

3. The name is absent

4. CAN CREDIT DEFAULT SWAPS PREDICT FINANCIAL CRISES? EMPIRICAL STUDY ON EMERGING MARKETS

5. The name is absent

6. EMU: some unanswered questions

7. The technological mediation of mathematics and its learning

8. Crime as a Social Cost of Poverty and Inequality: A Review Focusing on Developing Countries

9. The value-added of primary schools: what is it really measuring?

10. THE EFFECT OF MARKETING COOPERATIVES ON COST-REDUCING PROCESS INNOVATION ACTIVITY